# VALLURUPALLI NAGESWARA RAO VIGNANA JYOTHI INSTITUTE OF ENGINEERING AND TECHNOLOGY

An Autonomous, ISO 9001:2015 & QS I-Gauge Diamond Rated Institute, Accredited by NAAC with 'A++' Grade NBA Accreditation for B.Tech. CE, EEE, ME, ECE, CSE, EIE, IT Programmes

Approved by AICTE, New Delhi, Affiliated to JNTUH, NIRF 135<sup>th</sup> Rank in Engineering Category Recognized as "College with Potential for Excellence" by UGC

Vignana Jyothi Nagar, Pragathi Nagar, Nizampet (S.O), Hyderabad – 500 090, TS, India.

Telephone No: 040-2304 2758/59/60, Fax: 040-23042761

E-mail: postbox@vnrvjiet.ac.in, Website: www.vnrvjiet.ac.in

Estd.1995

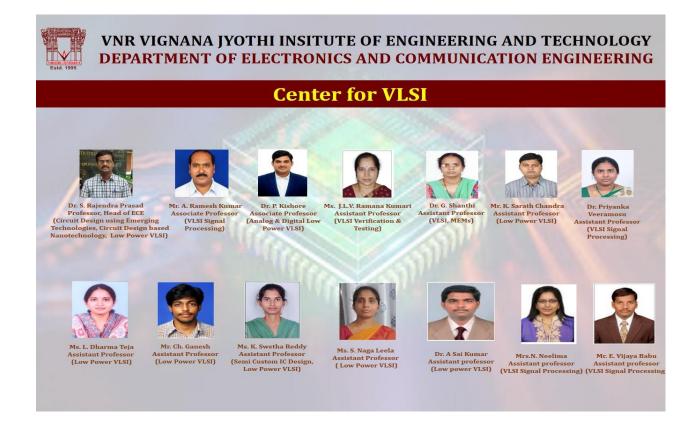

#### Department of ECE Center for VLSI

#### **About the Center**

The center for VLSI is established in the year 2010 with an objective of inculcating the reaerch culture in the field of VLSI among students and faculty. This center has spread its activities to research areas like Analog and Mixed Signal Design, Radio Frequency Integrated Circuit (RFIC) Design, Low-Power VLSI Design and Algorithms, etc. The center has PG programme in VLSI System Design with an intake of 18. A group of 14 faculty with the specialization of VLSI and, are working in the areas of Low Power VLSI, Design verification and testing, physical design, FPGA implementations of high performance systems and VLSI signal processing. One full time Ph.D scholar admitted under National Doctoral Fellowship offered by AICTE, India is working in the area of low power VLSI. The VLSI center is equipped with licensed softwares like Synopsys frontend and backend bundle, Mentor Graphics tool and latest FPGA kits.

#### Faculty associated with Center for VLSI

| S. No | Name of the faculty         | Designation               | Area of research                                                                                         |

|-------|-----------------------------|---------------------------|----------------------------------------------------------------------------------------------------------|

| 1     | Dr. S. Rajendra Prasad      | Professor, Head of<br>ECE | Circuit Design using Emerging<br>Technologies, Circuit Design<br>Based Nanotechnology, Low<br>Power VLSI |

| 2     | Mr. A. Ramesh Kumar         | Associate Professor       | VLSI Signal processing                                                                                   |

| 3     | Dr. P. Kishore              | Associate Professor       | Analog & Digital Low Power VLSI                                                                          |

| 4     | Ms. J.L.V. Ramana<br>Kumari | Assistant Professor       | VLSI Verification & Testing                                                                              |

| 5     | Ms. G. Shanthi              | Assistant Professor       | VLSI, MEMs                                                                                               |

| 6     | Mr. K. Sarath Chandra       | Assistant Professor       | Low Power VLSI                                                                                           |

| 7     | Dr. Priyanka<br>Veeramosu   | Assistant Professor       | VLSI Signal Processing                                                                                   |

| 8     | Ms. L. Dharma Teja          | Assistant Professor       | Low Power VLSI                                                                                           |

| 9  | Mr. Ch. Ganesh      | Assistant Professor | Low Power VLSI                           |

|----|---------------------|---------------------|------------------------------------------|

| 10 | Ms. K. Swetha Reddy | Assistant Professor | Semi-Custom IC Design, Low<br>Power VLSI |

| 11 | Ms. S. Naga Leela   | Assistant Professor | Low Power VLSI                           |

| 12 | Mrs. N.Neelima      | Assistant Professor | VLSI Signal processing                   |

| 13 | Dr. A Sai Kumar     | Assistant Professor | Low power VLSI                           |

| 14 | Mr. E. Vijaya Babu  | Assistant Professor | VLSI Signal processing                   |

#### **Facilities**

Center for VLSI has two laboratories with the following softwares and hardware kits. The facilities are available for all faculty and students who would like to participate in VLSI R&D activities.

#### **Softwares**

- Xilinx Vivado System Edition Software

- Mentor Graphics HEP1 Tool

- Synopsis Tool

#### Hardware Kits

| • | Atlys Spartan 6 FPGA Kit             | : 05 |

|---|--------------------------------------|------|

| • | Artix-7 Nexys 4 DDR Kit              | : 02 |

| • | Zynq Board(Zynq Zed Development Kit) | : 01 |

| • | Zynq Video And Image Processig Kit   | : 01 |

| • | Zynq 7000epp Evaluation Kit          | : 01 |

| • | Spartan 605 Kit                      | : 01 |

| • | Spartan 3E FPGA Kit                  | : 01 |

| • | Anvyl Kit                            | : 01 |

# Funded research projects carried out in center for VLSI

| S.No | Title of the Project                                                                                                                    | Funding Agency               | Sanctioned<br>Amount in<br>Lakhs | Faculty<br>Associated                                            |

|------|-----------------------------------------------------------------------------------------------------------------------------------------|------------------------------|----------------------------------|------------------------------------------------------------------|

| 1    | Design an FFT/IFFT IPcore with run-time configurable FFT size and data type and compile time configurable data type and data precision. | MMRFIC Technologies Pvt. Ltd | 2.0                              | Mr. Ch.<br>Ganesh                                                |

| 2    | Development of low power and<br>high speed FPGA based IP core<br>mini Ace architecture compatible<br>to data device corporation         | AICTE/RPS                    | 14.35                            | Dr.P.Kishore                                                     |

| 3    | IP Core Development Of MIL<br>STD 1553 for RT and MT<br>Terminals"                                                                      | Ananth<br>Technologies Ltd   | 4.24                             | Dr.P.Kishore<br>Mr.K.Sarath<br>Chandra<br>Mrs.K.Sweth<br>a Reddy |

### **Faculty as Resourse Persons**

| S.<br>No. | Name of the program      | Lecture Topic                                                                                                                                                                                                                                            | Name of the Faculty      | Duration                        | Venue                                                         | Organized by                                                  |

|-----------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|---------------------------------|---------------------------------------------------------------|---------------------------------------------------------------|

|           | Webinar                  | Strategies and tools to avoid plagiarism                                                                                                                                                                                                                 | Dr.Ranjan K<br>Senapathi | 23-06-2021                      | VVP Institute<br>of Engineering<br>and                        | VVP Institute<br>of Engineering<br>and                        |

| 1         | Guest Lecture            | Introduction to<br>Communication &<br>Signal Processing                                                                                                                                                                                                  | Dr.S.Rajendr<br>a Prasad | 03-06-2021                      | Technology Annamacharya Institute of Technology and Sciences, | Technology Annamacharya Institute of Technology and Sciences, |

| 2         | VLSI Training<br>Program | VLSI Evolution and<br>Recent trends in<br>VLSI industry                                                                                                                                                                                                  | K.Sarath<br>Chandra      | 17-05-2021<br>to 28-07-<br>2021 | Kadapa, AP Dept. of ECE, VNRVJIET                             | Kadapa, AP<br>VNRVJIET                                        |

| 3         | VLSI Training<br>Program | FPGA Design Flow ASIC Design Flow Designing with FPGAs Hands on session with Verilog HDL IC Design Flow- Semicustom and Full custom design- Hands on Session Overview of Digital Design Introduction to Verilog HDL, Language Constructs and Conventions | K.Naresh                 | 17-05-2021<br>to 28-07-<br>2021 | Dept. Of ECE,<br>VNRVJIET                                     | VNRVJIET                                                      |

|           | VLSI Training<br>Program | Gate Level Modeling  Designing with Pseudo NMOS, NMOS enhancement and Depletion mode transistors  CMOS,Pass Transitor Logic, Complementary PTL, Transmission Gate Logic Data Flow Level Modeling                                                         | Dr.P.Kishore             | 17-05-2021<br>to 28-07-<br>2021 | Dept. Of ECE,<br>VNRVJIET                                     | VNRVJIET                                                      |

| 5         | VLSI Training            | Behavioral Modeling                                                                                                                                                                                                                                      | K.Swetha                 | 17-05-2021                      | Dept. Of ECE,                                                 | VNRVJIET                                                      |

| 6         | Program                  | Hands on Sessions on Digital Design 7with Verilog Functions, Tasks, and User-Defined Primitives                                                                                                                                                          | Reddy                    | to 28-07-<br>2021               | VNRVJIET                                                      |                                                               |

| 7         | VLSI Training            | FF Conversions & Synchronous                                                                                                                                                                                                                             | J.L.V.Raman<br>a Kumari  | 17-05-2021<br>to 28-07-         | Dept. of ECE,<br>VNRVJIET                                     | VNRVJIET                                                      |

|          | T                  | T                    | T            | T          | T             |                                                  |

|----------|--------------------|----------------------|--------------|------------|---------------|--------------------------------------------------|

|          | Program            | Asynchronous         |              | 2021       |               |                                                  |

|          |                    | counter Design       |              |            |               |                                                  |

|          |                    | Mealy and Moore      |              |            |               |                                                  |

|          |                    | type FSMs with       |              |            |               |                                                  |

|          |                    | examples             |              |            |               |                                                  |

|          |                    | Introduction to      |              |            |               |                                                  |

|          |                    | Design of Controller |              |            |               |                                                  |

|          |                    | and Data path        |              |            |               |                                                  |

|          |                    | systems.             |              |            |               |                                                  |

|          |                    | Design of serial     |              |            |               |                                                  |

|          |                    | Receiver and         |              |            |               |                                                  |

|          |                    | Transmitter          |              |            |               |                                                  |

|          |                    | Sequence detector    |              |            |               |                                                  |

|          |                    | design.              |              |            |               |                                                  |

|          | VLSI Training      | Hands on Sessions    | Ch. Ganesh   | 17-05-2021 | Dept. of ECE, | VNRVJIET                                         |

|          | _                  | on Digital Design    | Cii. Ganesii | to 28-07-  | VNRVJIET      | VIVICVIILI                                       |

| 0        | Program            | with Verilog         |              | 2021       | VINICVIILI    |                                                  |

| 8        |                    |                      |              | 2021       |               |                                                  |

|          |                    | IC Design Flow-      |              | 17 05 2021 | D             | \$ 1\$ 15 \$ 15 \$ 15 \$ 15 \$ 15 \$ 15 \$ 15 \$ |

|          | TH CLEE            | Semicustom and Full  | <i>p</i> «   | 17-05-2021 | Dept. of ECE, | VNRVJIET                                         |

|          | VLSI Training      | custom design-       | Dr.S.        | to 28-07-  | VNRVJIET      |                                                  |

|          | Program            | Hands on Session     | Rajendra     | 2021       |               |                                                  |

|          |                    | MOS FET              | Prasad       |            |               |                                                  |

| 9        |                    | Characteristics      |              |            |               |                                                  |

|          |                    | CMOS inverter -      |              |            |               |                                                  |

|          |                    | static and dynamic   |              | 17-05-2021 | Dept. of ECE, | VNRVJIET                                         |

|          | IoT training       | characteristics      | Aytha        | to 28-07-  | VNRVJIET      |                                                  |

|          | Program            |                      | Ramesh       | 2021       |               |                                                  |

|          | Trogram            |                      | Kumar        |            |               |                                                  |

| 10       |                    |                      | Kuillai      |            |               |                                                  |

| 10       | 5-Day Online       | Design of serial     | Dr.S.Rajendr | 25-01-2021 | KL University | KL University                                    |

|          | •                  | Receiver and         |              | to 29-01-  | KL University | KL University                                    |

|          | National Workshop  | Transmitter          | a Prasad     | 2021.      |               |                                                  |

|          | on "Recent Trends  | Transmitter          |              | 2021.      |               |                                                  |

|          | in Microelectronic |                      |              |            |               |                                                  |

|          | Devices, VLSI      |                      |              |            |               |                                                  |

|          | Circuits and their |                      |              |            |               |                                                  |

|          |                    |                      |              |            |               |                                                  |

| 11       | applications-      |                      |              |            |               |                                                  |

| - 11     | National Level     | Recent trends in     | Dr.S.Rajendr | 28-12-2020 | Sridevi       | Sridevi                                          |

|          |                    |                      |              | to 31-12-  | Women's       | Women's                                          |

|          | Faculty            | Electronics and      | a Prasad     |            |               |                                                  |

|          | Development        | Communications       |              | 2020       | Engineering   | Engineering                                      |

|          | Programme on "     |                      |              |            | College       | College                                          |

|          | Recent trends in   |                      |              |            |               |                                                  |

|          | Electronics and    |                      |              |            |               |                                                  |

|          | Communications     |                      |              |            |               |                                                  |

|          |                    |                      |              |            |               |                                                  |

|          | for Teaching       |                      |              |            |               |                                                  |

|          | Learning and       |                      |              |            |               |                                                  |

|          | Research"          |                      |              |            |               |                                                  |

| 12       |                    |                      |              |            |               |                                                  |

|          | Two day webinar    | Evolution of         | Dr. S.       | 27-06-2020 | G.Pulla Reddy | G.Pulla Reddy                                    |

|          | on "Present Trends | Wireless             | Rajendra     |            | Engineering   | Engineering                                      |

|          | and Research       | Technologies         | Prasad       |            | College,      | College,                                         |

|          |                    | Technologies         | 110300       |            | Kurnool.      | Kurnool.                                         |

|          | scopes in SG       |                      |              |            |               |                                                  |

|          | Wireless           |                      |              |            |               |                                                  |

|          | Communications     |                      |              |            |               |                                                  |

| 13       |                    |                      |              |            |               |                                                  |

|          | RTL design and     | VLSI Evolution and   | K. Sarath    | 09-06-2020 | Dept. of ECE, | VNRVJIET                                         |

| 14       |                    | Recent trends in     |              |            | VNRVJIET      |                                                  |

| <u> </u> | İ                  | 1                    | l .          | 1          | l             |                                                  |

|    | verification                                               | VLSI industry                                              | Chandra                     |                                 |                                   |           |

|----|------------------------------------------------------------|------------------------------------------------------------|-----------------------------|---------------------------------|-----------------------------------|-----------|

| 15 |                                                            | Classification of IC<br>Design                             | K. Sarath<br>Chandra        | 16-06-2020                      |                                   |           |

| 16 | RTL design and verification                                | Controller design using FSMs                               | J LV Ramana<br>kumari       | 12-06-2020                      | Dept. of ECE,<br>VNRVJIET         | VNRVJIET  |

| 17 | RTL design and verification                                | VLSI Design<br>flow(FPGA& ASIC)                            | K. Naresh                   | 17-06-2020                      | Dept. of ECE,<br>VNRVJIET         | VNRVJIET  |

| 18 |                                                            | Behaviour modelling<br>style of Verilog<br>HDL (Hands-on)  |                             | 19-06-2020                      |                                   |           |

| 19 | RTL design and verification                                | Structural Modelling<br>style of Verilog<br>HDL (Hands-on) | Ch. Ganesh                  | 22-06-2020                      | Dept. of ECE,<br>VNRVJIET         | VNRVJIET  |

| 20 |                                                            | FPGA implementation of Digital system(Case Study)          |                             | 25-06-2020                      |                                   |           |

|    | RTL design and verification                                | Importance of Verilog HDL in Digital Design Automation     | K. Swetha<br>Reddy          | 18-06-2020                      | Dept. Of ECE,<br>VNRVJIET         | VNRVJIET  |

|    |                                                            | Synthesizable Verilog HDL for FSM(Hands-on)                |                             | 23-06-2020                      |                                   |           |

| 21 |                                                            | Design Verification using Testbench(Hands-on)              |                             | 24-06-2020                      |                                   |           |

| 21 | Embedded Systems,<br>Smart Sensors for<br>IOT Applications | Overview on wireless sensors                               | Dr.S.<br>Rajendra<br>Prasad | 17-09-2018<br>to 20-09-<br>2018 | Department of<br>ECE,<br>VNRVJIET | VNR VJIET |

| 23 | Embedded Systems,<br>Smart Sensors for<br>IOT Applications | FPGA & SoC Based<br>Embedded Systems<br>Designs            | A.Ramesh<br>Kumar           | 17-09-2018<br>to 20-09-<br>2018 | Department of<br>ECE,<br>VNRVJIET | VNR VJIET |

### Faculty as Reviewers and Editorial board members

| S. No. | Name of the faculty     | Nature of<br>Contribution                    | Details of associated Organization /<br>Journal / Conference etc.                                                                |

|--------|-------------------------|----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

|        | Dr.S.Rajendra<br>Prasad | Editorial<br>Board member                    | International Journal of VLSI Design & Communication System (VLSICS).                                                            |

|        |                         | Reviewer                                     | Heliyon – a peer-reviewed open access journal - indexed by Scopus.                                                               |

|        |                         | Guest Editor                                 | International Journal of Sensors and<br>Sensor Networks (IJSSN) - Journal                                                        |

|        |                         | Reviewer                                     | International journal of Circuit Theory and Applications                                                                         |

|        |                         |                                              | IEEE - Transactions on Devices and<br>Materials Reliability                                                                      |

| 1.     |                         |                                              | Elsevier - Microelectronics Journal                                                                                              |

|        |                         |                                              | Springer - Journal of Computational<br>Electronics                                                                               |

|        |                         |                                              | Springer Journal – Soft Computing                                                                                                |

|        |                         |                                              | International Journal of Speech Technology (IJST)                                                                                |

|        |                         |                                              | International Journal of VLSI Design & Communication Systems                                                                     |

|        |                         | Board of<br>Studies<br>Member                | Kesav memorial Institute of Technology, Hyderabad                                                                                |

|        | Dr.P.Kishore            | Member                                       | CAS/EDS joint chapter, IEEE Hyderabad Section                                                                                    |

| 2.     |                         | Member,<br>Technical<br>Program<br>Committee | International Conference on<br>Artificial Intelligence: Theory and<br>Applications [AITA 2021]                                   |

|        |                         | Reviewer                                     | IEEE International Symposium on<br>Circuits and Systems (ISCAS),<br>Organizing by IEEE Circuits and<br>Systems Society at Japan. |

| 3.     | K.Naresh                | Reviewer                                     | IEEE Transactions on VLSI Systems                                                                                                |

### **Faculty Awards and Recognitions**

| S.No. | Name of the<br>Faculty | Designation         | Details of the award and recognition            |

|-------|------------------------|---------------------|-------------------------------------------------|

| 1     | Dr.S.Rajendra          | Professor           | Recognized as IEEE Senior Member                |

|       | Prasad                 |                     | One of the Toppers (In TOP 1%) in NPTEL         |

|       |                        |                     | exam on Microelectronics: Devices to Circuits   |

|       |                        |                     | conducted during July-October 2021.             |

| 2     | Dr.P.Kishore           | Associate           | Topper in NPTEL Exam –VLSI Signal               |

|       |                        | Professor           | Processing (January-April 2020) Exam            |

|       |                        |                     | conducted in October 2020.                      |

|       |                        |                     | Recognized as IEEE Senior Member in April       |

|       |                        |                     | 2020.                                           |

|       |                        |                     | Received Dr. Sarvepalli Radha Krishna           |

|       |                        |                     | Distinguished Scientist Award-2021in            |

|       |                        |                     | appreciation of the dedication and commitment   |

|       |                        |                     | in Technology and Research in ECE conferred     |

|       |                        |                     | on 5 <sup>th</sup> September 2021 by Center for |

|       |                        |                     | Professional Advancement Continuous             |

|       |                        |                     | Education(CPACE)                                |

| 3     | Dr.V.Priyanka          | Assistant Professor | Recognized as IEEE Senior Member in Apr         |

|       |                        |                     | 2020.                                           |

|       |                        |                     | Received an Exemplary Student Branch Award      |

|       |                        |                     | from IEEE Hyderabad section Student Activity    |

|       |                        |                     | Committee on 4th December 2021                  |

## **Faculty Guiding PhD scholars**

|          | Name           |              | Ph.D.                                           | Research                        | ls                                             |                             |             |

|----------|----------------|--------------|-------------------------------------------------|---------------------------------|------------------------------------------------|-----------------------------|-------------|

| S.<br>No |                | Specializati | Details -<br>(University<br>& Year of<br>Award) | Name of the<br>Research Scholar | Year of<br>Admission<br>and / or<br>Completion | University                  | Status      |

|          |                |              |                                                 | S.Sravanthi                     | 2017                                           | JJTU,<br>Rajasthan          | On<br>going |

|          | Dr.S.<br>Rajen | I OW POWER   | HNTTH 2015                                      | Uma Maheswar                    | 2019                                           | AICTE-<br>NDF               | On<br>going |

| 1        | dra<br>Prasad  | VLSI         |                                                 | L.Dharma Teja                   | 2011                                           | JNTUH                       | On<br>going |

|          | 11 1asau       | Tasau        |                                                 | Prasanna Kumar G                | 2017                                           | SSSUT&M<br>S, Sehore,<br>MP | On<br>going |

# **Details of Faculty Professional Body Memberships**

| S.<br>No | Faculty Name            | Membership No. |              |              |      |               |                     |                  |

|----------|-------------------------|----------------|--------------|--------------|------|---------------|---------------------|------------------|

| NO       |                         | IEEE           | ISTE         | IETE         | ISOI | IEI           | Internet<br>Society | OTHERS           |

| 1        | Dr.S.Rajendra<br>Prasad | SM921755<br>69 | LM<br>107789 | M20225       | -    | -             | -                   | -                |

| 2        | A.Ramesh Kumar          | -              | LM62868      | M15983       | -    | -             | -                   |                  |

| 3        | J.L.V.Ramana<br>Kumari  | 97531144       | LM62871      | M23446<br>4  | -    | -             | -                   | -                |

| 4        | Dr.L.V.Rajani<br>Kumari | 97511211       | LM79575      | M23447       | -    | -             | 2236865             | IAENG:2933<br>59 |

| 5        | L.Dharma Teja           | -              | LM79578      | M23447<br>3  | -    | -             | -                   | -                |

| 6        | G.Shanthi               | -              | LM<br>107791 | -            | -    | -             | 2236857             | IAENG:<br>293351 |

| 7        | Dr. V. Priyanka         | SM951454<br>16 | LM90973      | AM234<br>512 | -    | -             | 2229846             | IAENG:2933<br>57 |

| 8        | Dr. P. Kishore          | SM951453<br>72 | LM71521      | AM198<br>519 | -    | AM10017<br>04 | -                   | -                |

| 9        | K.Sharath Chandra       | -              | LM<br>107792 | -            | -    | -             | 2236868             | IAENG:2933<br>71 |

| 10       | Ch.Ganesh               |                | LM<br>122048 | -            | -    | -             | -                   |                  |

|          | K.Swetha Reddy          | 97531079       | LM<br>122058 | -            | -    | -             | 2236863             | IAENG:2933<br>33 |

|          | S.Naga Leela            | -              | LM<br>107784 | -            | -    | -             | -                   | IAENG:2933<br>63 |

#### **Industry interactions**

#### List of MOUs with VLSI industries

| Sl. No. | Name of the industry     | Impact                                                                                                                                                                                                                                  |

|---------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | Ananth Technologies Ltd. | Sanctioned consultancy project on "IP Core<br>Development of MIL STD 1553 for RT and MT<br>terminals" for an amount of Rs.4.24 Lakhs.                                                                                                   |

| 2       | AMD Ltd                  | P.G (VLSI System Design) students got internship opportunities in VLSI domine during academic year                                                                                                                                      |

| 3       | AVANTEL Ltd              | Dr. A. Vidyasagar, Managing Director is a member of BoS and involving in design the syllabus of courses under communication module.                                                                                                     |

| 4       | TCS, Hyderabad           | <ul> <li>Remote Internships are provided to the students.</li> <li>P.G (VLSI System Design) students got internship opportunities in VLSI domine during academic year 2021-22, , which is a new initiative of TCS Hyderabad.</li> </ul> |

#### List of Industry personels associated

- 1. Mr. Venu Gopal Bhat, Director of Engineering, Automotive SW, NVIDIA, Bangalore

- 2. Mr. Lakshmi Narayana kamarthi, Principal Engineer, NXP India Private Limited,Bangalore

- 3. Mr. K.Balaji, Director of Physical Design, SiFive Ltd, Bangalore

- 4. Mrs. Vijitha Challa, Pre-Si valid/verif engineer, INTEL, Hyderabad

- 5. Mr.D. Sreekanth, Application Engineer, AMD India Private Limited, Hyderabad

- 6. Mr. Tummuri Bala Surya Sriramachandra Pavan Kumar, Soc Design Engineer, INTEL

- 7. Mr.S.Krishna Teja, Staff Engineer, Mentor Graphics, Hyderabad

- 8. Mr. Yadagiri D, Sr. Silicon Design Engineer, AMD India Private Limited, Hyderabad

- 9. Mr.Bala Krishna ,Synopsys,Hyderabad

- 10. Mr. Sai Teja Mannam, SoC Design Engineer, Intel, Hillsboro, Oregon, USA

- 11. Dr.E.Lakshmi Prasad, Senior DFT Engineer, Tessolve semiconductor Pvt. Ltd, Bangalore

- 12. Mr. Suresh Nagula, SR II, R&D Engineer, Synopsys Inc, Hyderabad

- 13. Dr. Srinivas, Design Engineer, Micron Technology Inc, Hyderabad

- 14. Nagalatha Ramineni, Systems Design Manager, AMD India Private Limited, Hyderabad

- 15. Dr.A.G.Krishnaknath, Senior Manager, AMS Semiconductors Pvt Ltd, Hyderabad.

### Guest lectures delivered by Industry experts during last 3 Years

| S.No | Name of the industry personal | Industry associated                       | Title                                                                             | Date           |

|------|-------------------------------|-------------------------------------------|-----------------------------------------------------------------------------------|----------------|

| 1    | Mr. s. Krishna<br>Teja        | Siemens EDA,<br>Hyderabad                 | Design Challenges in<br>Digital VLSI                                              | 25th June 2022 |

| 2    | Mr. D.Yadagiri                | Advanced Micro Devices(AMD)Ltd, Hyderabad | Bridging gap between Industry and Academia                                        | 29-08-2020     |

| 3    | Mr.Y.Avinash                  | Mirafra Technologies<br>Ltd, Bangalore    | Engineering Education - Match Your Passion - Charting the Right Career Choice     | 19-09-2020     |

| 4    | Mr.D. Srikanth                | Xilinx, Hyderabad                         | Carrier Opportunities                                                             | 19-12-2020     |

| 5    | Ms. Sushmitha Ch              | Synopsys, Hyderabad                       | Experience & Tips During Placements, Balancing and Learning During Post Placement | 02-06-2021     |

| 6    | Mr.Yadagiri                   | Advanced Micro Devices(AMD)Ltd, Hyderabad | Motivating the students towards the Carrier in VLSI Industry                      | 23-11-2019     |

Guest Lecture delivered on "Opportunities and Challenges in VLSI Industry" by Mr.Lakshmi Narayana Kamarthi

Guest Lecture delivered on "Carrier Opportunities" by Mr.D. Srikanath

### Internships Opportunities in VLSI related industries

| S.No | Name of the Industry           | Name of the Student & Roll No       |  |  |

|------|--------------------------------|-------------------------------------|--|--|

| 1    | Synopsys                       | Sahithi Kannaiahgari(17071A0421)    |  |  |

| 2    |                                | Shivani Samanapally(17071A0447)     |  |  |

| 3    |                                | Rohith Reddy Appidi(17071A0463)     |  |  |

| 4    |                                | Saadia Hassan(17071A0446)           |  |  |

| 5    |                                | Sai Sharan Morisetty(19075A0406)    |  |  |

| 6    |                                | Rupa Sreelekha M(18071A0493)        |  |  |

| 7    |                                | Samarth Raj G(18071A04B4)           |  |  |

| 8    |                                | Challapalli Ramakrishna(18071A04D3) |  |  |

| 9    | Advanced Micro Devices(AMD)    | Kota Murali Mohan(20071D5703)       |  |  |

| 10   |                                | Y Sravya Mounika(20071D5711)        |  |  |

| 11   |                                | Adapa Naga Sai Nikhil(18071D5701)   |  |  |

| 12   | TCS                            | Sai Teja Tuduru(20071D5708)         |  |  |

| 13   | _                              | M. Sai Greeshma(19071D5708)         |  |  |

| 14   | Siliconus Technologies Pvt Ltd | Sainath Yarra(20071D5709)           |  |  |

| 15   |                                | Nagasani Rakesh(20071D5706)         |  |  |

| 16   |                                | Harsha Lourdu M(20071D5705)         |  |  |

| 17   |                                | Kacharla Sanjay(20071D5702)         |  |  |

| 18   | Mentor Graphics                | P.Sravanthi(19071D5711)             |  |  |

<sup>\*\*</sup>All the students are converted to full time employees

## **Academic projects carried out by Student Projects during 2021-22**

| Batch<br>No. | Roll No   Title of the Project                                      |                                                            | Name of the Supervisor |  |

|--------------|---------------------------------------------------------------------|------------------------------------------------------------|------------------------|--|

| 1            | 18071A0402                                                          | Multicock domain based watch dog timer for image           | •                      |  |

|              | 18071A0455                                                          | processor                                                  |                        |  |

|              | 18071A0411                                                          |                                                            | Ms.J.L.V.Ram           |  |

|              | 19075A0402                                                          |                                                            | ana Kumari             |  |

|              | 17071A0458                                                          |                                                            |                        |  |

| 2            | 18071A0401                                                          | Design and Analysis of CMOS two stage comparator           |                        |  |

|              | 18071A0413                                                          |                                                            | Dr.S.Rajendra          |  |

|              | 18071A0421                                                          |                                                            | Prasad                 |  |

|              | 18071A0424                                                          |                                                            |                        |  |

| 3            | 18071A0443                                                          | 15T SRAM cell using CNTFET,FINFET & GNRFET                 |                        |  |

|              | 418071A0403                                                         |                                                            | Ms.L.Dharma            |  |

|              | 18071A0418                                                          | 7                                                          | Teja                   |  |

|              | 18071A0405                                                          |                                                            |                        |  |

| 4            | 18071A0492                                                          | Design and Analysis of Logic Circuits Using Quantum Dot    |                        |  |

|              | 18071A04A6                                                          | Cellular Automata                                          | Ms.K.Swetha            |  |

|              | 18071A04B6                                                          |                                                            | Reddy                  |  |

|              | 18071A04B8                                                          |                                                            |                        |  |

| 5            | 18071A0478                                                          | Area Efficcient Adder using QCA                            |                        |  |

|              | 18071A0486                                                          |                                                            | Dr.P.Kishore           |  |

|              | 18071A0491                                                          |                                                            |                        |  |

|              | 18071A04A0                                                          |                                                            |                        |  |

| 6            | 18071A0462                                                          | Design and Analysis of Modified Strong-Arm Latch           |                        |  |

|              | 18071A0482                                                          | comparator                                                 | M. V.C. ala            |  |

|              | 18071A0493                                                          |                                                            | Ms.K.Swetha<br>Reddy   |  |

|              | 18071A0494                                                          |                                                            | Reddy                  |  |

|              | 18071A04A9                                                          |                                                            |                        |  |

| 7            | 18071A04A5 Impelemnatation of cascaded integrator comb filter using |                                                            |                        |  |

| 18071A04B4   |                                                                     | verilog hdl                                                | Ms.G.Shanthi           |  |

|              | 19075A0409                                                          |                                                            | Wis.G.Shahuli          |  |

|              | 19075A0410                                                          |                                                            |                        |  |

| 8            | 18071A0461                                                          | Design of AHBtoAPB Bridge for efficient power              |                        |  |

|              | 18071A0487                                                          | consumption                                                | Mr.K.Sarath            |  |

|              | 18071A0490                                                          |                                                            | Chandra                |  |

|              | 18071A04A1                                                          |                                                            |                        |  |

|              | 18071A0497                                                          | Low power and low area VD-FIR filter                       |                        |  |

| 9            | 18071A0476                                                          | 7                                                          |                        |  |

|              | 18071A0463                                                          | 7                                                          | Dr.V.Priyanka          |  |

|              | 18071A04C0                                                          |                                                            |                        |  |

|              | 16071A04A5                                                          |                                                            |                        |  |

| 10           | 18071A04F1                                                          | Design of Domino Comparator using CNTFET                   | Ms.S.Naga              |  |

|              | 18071A04C8                                                          | 1                                                          | Leela                  |  |

|              | 19075A0415                                                          | 1                                                          |                        |  |

|              | 18071A04E5                                                          |                                                            |                        |  |

| 11           | 18071A04D1                                                          | Dynamic Reconfigurable FIR filter for 5G Applications      | Mr.A.Ramesh            |  |

|              |                                                                     | 2 Jamine Reconfiguration 1 IR lines for 30 Applications    | Kumar                  |  |

| 11           | XI) /   AU4E3                                                       | 1                                                          | 1                      |  |

| 11           | 18071A04F3                                                          | _                                                          |                        |  |

| 11           | 18071A0H8                                                           |                                                            |                        |  |

|              |                                                                     | Design of Approximate divider arithemtic circuit for image | Mr.Ch.Ganesh           |  |

|    | 18071A04D7 |                                                          |               |

|----|------------|----------------------------------------------------------|---------------|

|    | 18071A04H1 |                                                          |               |

| 13 | 18071A04G3 | Design and analysis of cmos voltage controlled LC        | Dr.S.Rajendra |

|    | 18071A04C6 | Oscillator                                               | Prasad        |

|    | 18071A04F9 |                                                          |               |

|    | 18071A04D3 |                                                          |               |

| 14 | 18071A04C9 | Implementation of error detection and correction using   | Mr.Ch.Ganesh  |

|    | 18071A04G1 | viterbi decoding                                         |               |

|    | 18071A04H6 |                                                          |               |

|    | 18071A04J0 |                                                          |               |

| 15 | 18071A04K1 | Design of FIR filter based on retiming using vlsi design |               |

|    | 18071A04M7 | metrics                                                  | Dr.P.Kishore  |

|    | 18071A04N0 |                                                          | DI.F.KISHOTE  |

|    | 18071A04M9 |                                                          |               |

| 16 | 18071A04N5 | Design of 4-bit Approximate Dadda Multiplier for CNN     |               |

|    | 18071A04K7 | Applications                                             | Mr.K.Nareh    |

|    | 19075A0419 |                                                          | wir.K.Naren   |

|    | 18071A04M0 |                                                          |               |

## Best academic projects from the Center for VLSI for the academic year 2020-21

| S.No. | Project Title                                                                      | Roll Nos                                             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------|------------------------------------------------------------------------------------|------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | Design and Analysis of<br>Logic Circuits Using<br>Quantum Dot Cellular<br>Automata | 18071A0480<br>18071A0467<br>18071A04B3<br>18071A0469 | Quantum-dot Cellular Automata (QCA) is a substitution to Complementary Metal—Oxide—Semiconductor (CMOS) technology in nanoscale level. With technology scaling, high power consumption of design prevents the energy-efficient realization of complex logic circuits at nanoscale. This system works on the basis of electron interactions within quantum dots rather than columbic force. This paper mainly projects the design and analysis of results of various logic circuits using quantum dot cellular automata (QCA) designer.                                  |

| 2     | Design of FIR filter based<br>on retiming using vlsi<br>design metrics             | 18071A0492<br>18071A04A6<br>18071A04B6<br>18071A04B8 | Retiming is a VLSI design technique in which the positioning or the arrangement of the delay elements or registers is reorganized such that the critical path delay of the filter is reduced. The rearrangement and addition of registers is such that the functionality of the retimed FIR filter is same as that of the original filter. Simulation results are discussed in this project. Optimized FIR filters are hence designed using different retiming techniques by maintaining a tradeoff between the design metrics in comparison with the existing designs. |

## Outcome of the Student Academic projects(2021-2022)

### Papers published/communicated

| S.No | Title of the Paper                                                                     | Name of the<br>Conference/Journal                                                                                                          | <b>Conference Dates</b>      | Status of the paper(Submiited/Acc epted/Published)               |

|------|----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|------------------------------------------------------------------|

| 1.   | Convolution Merging Technique<br>For Image Encryption<br>Application                   | International Conference on<br>Recent Trends in<br>Microelectronics,<br>Automation, Computing<br>and Communication<br>Systems(ICMACC-2022) | 28-30<br>Decemebr 2022       | Accepted                                                         |

| 2.   | Analyzing Performance Metrics<br>of Low Power 15T Sram Cell<br>Using Finfet And GNRFET | IJARIIE-ISSN(O)-2395-<br>4396                                                                                                              | 2022                         | Published                                                        |

| 3.   | Area Efficient Logic Circuits using Quantun Dot Comuputation Automata                  | MIND 2022                                                                                                                                  | 21–22<br>December 2022       | Submitted                                                        |

| 4.   | Implemenation of area Efficient Adder using QCA                                        | International Conference on<br>Recent Trends in<br>Microelectronics,<br>Automation, Computing<br>and Communication<br>Systems              | 28–30<br>December 2022       | Accepted                                                         |

| 5.   | An Efficient FPGA Implementation of Cascade Integrator Comb Filter                     | ICIIET 2022                                                                                                                                | 22 - 24<br>September<br>2022 | Submitted                                                        |

| 6.   | Design of Ahb2apb Bridge For Efficient Power Consumption                               | International Conference on<br>Recent Trends in<br>Microelectronics,<br>Automation, Computing<br>and Communication<br>Systems              | 28–30<br>December 2022       | Submitted                                                        |

| 7.   | An Efficient Approach for<br>Denoising ECG Signal using<br>FIR Filter                  | 2022 International<br>Conference on Intelligent<br>Innovations in Engineering<br>and Technology (ICIIET)                                   | 22-24<br>September<br>2022   | Accepted                                                         |

| 8.   | Design and Analysis of<br>CNTFET Dynamic Comparator                                    | ICIECE-2022                                                                                                                                | DEC 16-<br>17,2022           | Submitted                                                        |

| 9.   | Implementation of Viterbi<br>Decoder for Error Detection and<br>Correction             | IJRTI-Volume 7, Issue 8                                                                                                                    | August-2022                  | Published                                                        |

| 10.  | Design of FIR filter based on retiming using vlsi design metrics                       | ARPN Journal of<br>Engineering and Applied<br>Sciences (JEAS)                                                                              | -                            | Submitted -<br>Estimated time of<br>publication-<br>January 2023 |